# NATIONAL OPEN UNIVERSITY OF NIGERIA

SCHOOL OF SCIENCE AND TECHNOLOGY

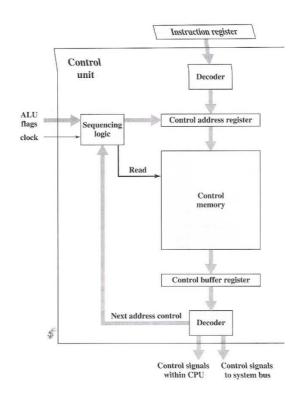

COURSE CODE: CIT309

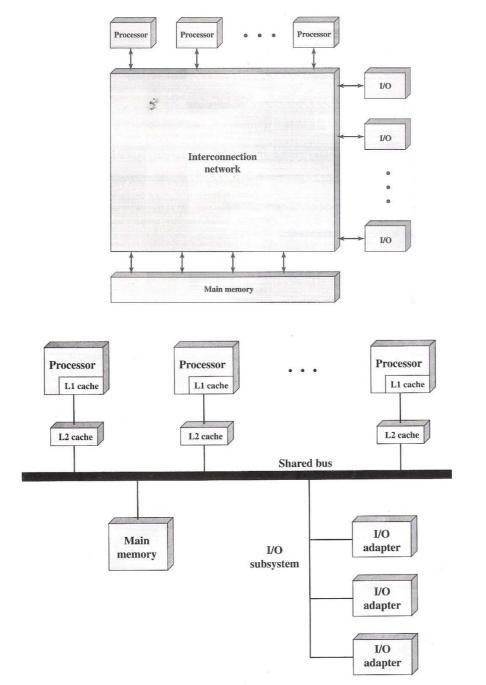

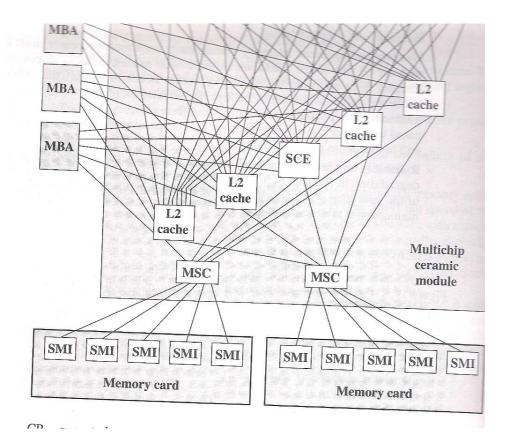

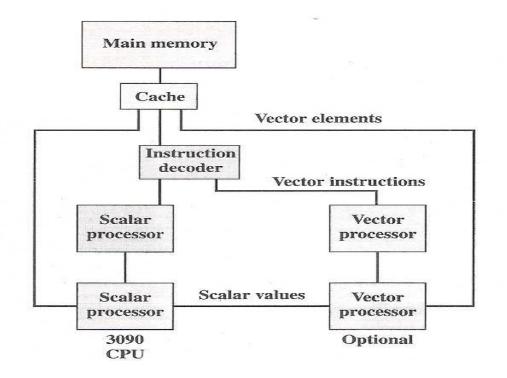

**COURSE TITLE:** Computer Architecture

CIT 309 COMPUTER ARCHITECTURE

**COURSE TEAM:**

Developer/Writer: Greg Onwodi National Open University of Nigeria

Course Coordinator: Rele Afolorunsho National Open University of Nigeria

Course Editor: Engr. C. Obi

Programme Leader : Prof. Afolabi Adebanjo National Open University of Nigeria

NATIONAL OPEN UNIVERSITY OF NIGERIA

CIT 309

National Open University of Nigeria Headquarters 14/16 Ahmadu Bello Way Victoria Island Lagos

Abuja Office No. 5 Dares Salaam Street Off Aminu Kano Crescent Wuse II, Abuja Nigeria

e-mail: central info@nou.edu.ng URL: www.nou.edu.ng Published By: National Open University of Nigeria Printed 2009

ISBN: All Rights Reserved

# CONTENTS

MODULE 1

| MODULEI | OKOANIZATION AND AKCHITECTOKE    |

|---------|----------------------------------|

|         |                                  |

| UNIT 1  | COMPUTER ORGANIZATION AND        |

|         | ARCHITECTURE                     |

| UNIT 2  | INSTRUCTION SETS CHARACTERISTICS |

|         | AND FUNCTIONS                    |

| UNITY 3 | TYPES OF OPERANDS                |

ORGANIZATION AND ARCHITECTURE

# **MODULE 2 COMPUTER ARITHMETIC**

| UNIT 1 | THE ARITHMETIC AND LOGIC UNIT |

|--------|-------------------------------|

| UNIT 2 | CONTROL UNIT DESIGN/          |

|        | IMPLEMENTATION                |

# **MODULE 3 PARALLEL ORGANIZATION**

- UNIT 2 SYMMETRIC MULTI PROCESSOR

- UNIT 3 MULTI THREADING AND CHIP MULTI PROCESSOR

- UNIT 4 VECTOR COMPUTATION

# MODULE 4 REDUCED INSTRUCTION SET COMPUTERS

UNIT 1 INSTRUCTION EXECUTION CHARACTERISTIC UNIT 2 REDUCED INSTRUCTION SET ARCHITECTURE UNIT 3 RISC PIPELING UNIT MIPS 4000

# MODULE 5 OPERATING SYSTEM SUPPORT ERROR DETECTION AND ERROR CORRECTION CODING

UNIT 1 OPERATING SYSTEM OVERVIEW UNIT 2 SCHEDULING UNIT 3 MEMORY SYSTEM UNIT 4 CACHE MEMORY

#### **MODULE DIGITAL LOGIC**

UNIT 1 BOOLEAN ALGEBRA UNIT 2 LOGIC OPERATIONS UNIT 3 COMBINATIONAL CIRCUITS

# MODULE 1: ORGANIZATION AND ARCHITECTURE UNIT 1: COMPUTER ORGANIZATION AND ARCHITECTURE UNIT 2: INSTRUCTION SETS CHARACTERISTICS AND FUNCTIONS UNIT 3: TYPES OF OPERANDS

# UNIT 1 1.0 INTRODUCTION 2.0 OBJECTIVES 3.0 MAIN CONTENTS 3.1 COMPUTER ORGANIZATION AND ARCHITECTURE 3.2 STRUCTURE AND FUNCTION 3.3 COMPUTER COMPONENTS 4.0 CONCLUSION 5.0 SUMMARY 6.0 TUTOR MARKED ASSIGNMENT 7.0 REFERENCES/FURTHER READING

#### **1.0 INTRODUCTION**

In spite of the variety and pace of change in the computer field, certain fundamental concepts apply consistently throughout. To be sure, the application of these concepts depends on the current state of technology and the price/ performance objectives of the designer.

Many computer manufacturers offer a family of computer models, all with the same architecture but with differences in organization. In a class of computers called microcomputers, the relationship between the architecture and organization is very close. Changes in technology not only influence organization but also result in the introduction of more powerful and more complex architecture. However, because a computer organization must be

designed o implement a particular architectural specification, a thorough treatment of organization requires a detailed examination of architecture as well.

# 2.0 **OBJECTIVES**

At the end of this unit you should be able to:

• Explain the operational units of a computer system.

• Outline types of operands and operations specific by machine instruction.

• Explain opcodes, operands and addressing modes

#### 3.0 MAIN CONTENT

#### 3.1 COMPUTER ORGANIZATION AND ARCHITECTURE

Although it is difficult to give precise definition, a consensus exists about the general area covered by it. Computer organization refers to the operational units and their interconnection that realize the architectural specification. Examples of architectural attributes include the instruction set, the number of bit used to represent various data types (e. g numbers, characters), I/O mechanism, and techniques for addressing memory. Organizational attributes include those hardware details transparent to the programmer, such as control signals; interfaces between the computer peripherals and memory technology used.

#### 3.2 STRUCTURE AND FUNCTION

A computer is a computer system, contemporary computers contain millions of elementary electronic components.

• **Structure:** The way in which the components are interrelated.

• **Function:** The operation of each individual component as part of the structure.

In term of description, there are two choices: starting at the bottom and building up to a complete description, or beginning with a top view and decomposing the system into its subparts. Evidence from a number of fields suggest that the top down approach is the clearest and most effective. The approach taken is that the computer be described from the top down.

Both the structure and functioning of a computer are simple. Figure 1.1 depicts the basic functions that a computer can perform. In general terms, there are only four:

- Data processing

- Data storage

- Data movement

- Control

The computer of course, must be able to process data. The data may take a wide variety of forms, and the range of processing requirements id broad. It is also essential that a computer store data. Even if the computer is processing data on the fly (i.e data come in and get processed and the results go out immediately) the computer must temporarily store at least. Those pieces of data that are being worked on at any given moment. Files of data are stored on the computer for subsequent retrieval and update.

The computer must be able to move data between itself an outside world. The computers operating environment consist of devices that serve as either sources or destinations of data. When data are received from or delivered to a device that is directly connected to the computer, the process is known as input- output (I/O), and the device is referred to as a peripheral. When data are moved over longer distances, to or form a remote device, the process is known as data communications. Finally, there must be control of these three functions. Ultimately, this control is exercised by the individuals who provide the computer with instructions. Within the computer a control unit manages the computers resources and orchestrates the performance of its functional parts in response to those instructions.

There are four main structural components

- **Central processing unit** (**CPU**): Controls the operations of the computer and performs its data processing functions; often simply referred to as processor.

- Main memory: Stores data

- **I/O:** Moves data between the computer and its external environment.

- **System interconnections**: Some mechanism that provides for communication among CPU, main memory and I/O. A common example of system interconnection is by means of a system bus, consisting of a number of conducting wires to which all the other components attach.

However, the most interesting and complex component is the C. P. U. Its major structural components are as follows:

- **Control unit**: Controls the operations of the CPU and hence the computer.

- Arithmetic and logic unit (ALU): Performs the computer data processing functions.

- Registers: Provides storage internal to the CPU.

- **CPU** interconnection: Some mechanism that provides for communication among the control unit, ALU and registers.

#### **COMPUTER COMPONENTS**

As discussed in Chapter 2, virtually all contemporary computer designs are based on concepts developed by John yon Neumann at the Institute for Advanced Studies Princeton. Such a design is referred to as the *yon Neumann architecture* and is base on three key concepts:

- Data and instructions are stored in a single read-write memory.

- The contents of this memory are addressable by location, without regard to the type of data contained there.

- Execution occurs in a sequential fashion (unless explicitly modified) from one instruction to the next.

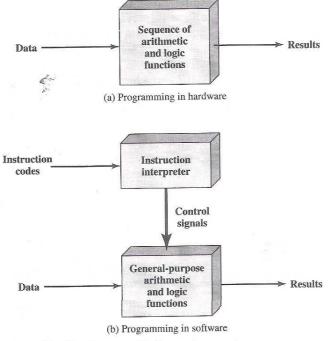

The reasoning behind these concepts was discussed in Chapter 2 but is worth summarizing here. There is a small set of basic logic components that can be combined in various ways to store binary data and to perform arithmetic and logical operations on that data. If there is a particular computation to be performed, a configuration of logic components designed specifically for that computation could be constructed. We can think of the process of connecting the various components in the desired configuration as a form of programming. The resulting "program" is in the form of hardware and is termed a *hardwired program*.

Now consider this alternative. Suppose we construct a general-purpose configuration of arithmetic and logic functions. This set of hardware will perform various functions on data depending on control signals applied to the hardware. In the original case of customized hardware, the system accepts data and produces results (Figure 3.1a). With general-purpose hardware, the system accepts data and control signals and produces results. Thus, instead of rewiring the hardware for each new program, the programmer merely needs to supply a new set of control signals.

How shall control signals be supplied? The answer is simple but subtle. The entire program is actually a sequence of steps. At each step, some arithmetic or logical

operation is performed on some data. For each step, a new set of control signals is needed. Let us provide a unique code for each possible set of control signals, and let us add to the general-purpose hardware a segment that can accept a code and generate control signals (Figure 3.1b).

Programming is now much easier. Instead of rewiring the hardware for each new program, all we need to do is provide a new sequence of codes. Each code is, in effect, an instruction, and part of the hardware interprets each instruction and generates control signals. To distinguish this new method of programming, a sequence of codes or instructions is called *software*.

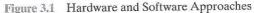

Figure 3.1b indicates two major components of the system: an instruction interpreter and a module of general-purpose arithmetic and logic functions. These two constitute the CPU. Several other components are needed to yield a functioning computer. Data and instructions must be put into the system. For this we need some sort of input module. This module contains basic components for accepting data anc instructions in some form and converting them into an internal form of signals usable by the system. A means of reporting results is needed, and this is in the form o an output module. Taken together, these are referred to as I10 *components*.

One more component is needed. An input device will bring instructions an` data in sequentially. But a program is not invariably executed sequentially; it ma,. jump around (e.g., the IAS jump instruction). Similarly, operations on data may require access to more than just one element at a time in a predetermined sequence Thus, there must be a place to store temporarily both instructions and data. That module is called *memory*, or *main memory* to distinguish it from external storage of peripheral devices. Von Neumann pointed out that the same memory could be uses to store both instructions and data.

Figure 3.2 illustrates these top-level components and suggests the interaction, among them. The CPU exchanges data with memory. For this purpose, it typical" makes use of two internal (to the CPU) registers: a memory address register (MAR), which specifies the address in memory for the next read or write, and memory buffer register (MBR), which contains the data to be written into memory receives the data read from memory. Similarly, an I/0 address register (I/OAR specifies a particular 1/0 device. An I/0 buffer (I/OBR) register is used for the <sub>ex</sub>change of data between an I/0 module and the CPU.

A memory module consists of a set of locations, defined by sequentially nun bered addresses. Each location contains a binary number that can be interpreted either an instruction or data. An 1/0 module transfers data from external devices CPU and memory, and vice versa. It contains internal buffers for temporarily holing these data until they can be sent on.

Having looked briefly at these major components, we now turn to an over view of how these components function together to execute programs.

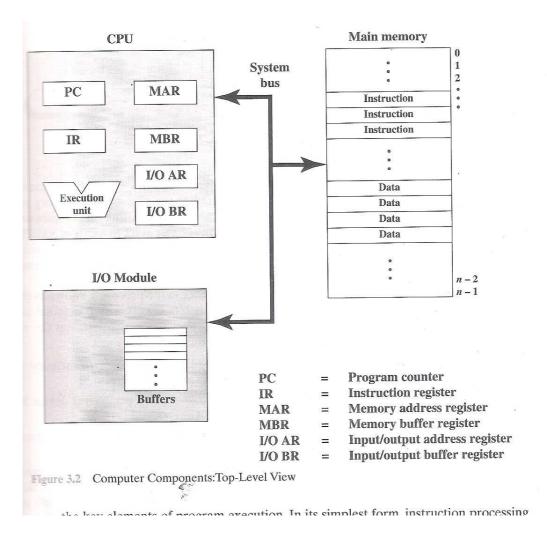

the key elements of program execution. In its simplest form, instruction processing consists of two steps: The processor reads *(fetches)* instructions from memory one at a time and executes each instruction. Program execution consists of repeating the process of instruction fetch and instruction execution. The instruction execution may involve several operations and depends on the nature of the instruction (see, for example, the lower portion of Figure 2.4).

The processing required for a single instruction is called an *instruction* cycle. Using the simplified two-step description given previously, the

instruction cycle is depicted in Figure 3.3. The two steps are referred to as the *fetch cycle* and the *execute*

*cycle.* Program execution halts only if the machine is turned off, some sort of unrecoverable error occurs, or a program instruction that halts the computer is encountered.

#### **INSTRUCTION FETCH AND EXECUTE**

At the beginning of each instruction cycle, the processor fetches an instruction from memory. In a typical processor, a register called the program counter (PC) holds the address of the instruction to be fetched next. Unless told otherwise, the processor

Basic Instruction Cycle

always increments the PC after each instruction fetch so that it will fetch the next instruction in sequence (i.e., the instruction located at the next higher memory address). So, for example, consider a computer in which each instruction occupies one 16-bit word of memory. Assume that the program counter is set to location 300. The processor will next fetch the instruction at location 300. On succeeding instruction cycles, it will fetch instructions from locations 301, 302, 303, and so on. This sequence may be altered, as explained presently.

The fetched instruction is loaded into a register in the processor known as the instruction register (IR). The instruction contains bits that specify the action the processor is to take. The processor interprets the instruction and performs the required action. In general, these actions fall into four categories:

Processor-memory: Data may be transferred from processor to memory or from memory to processor.

Processor-I/O: Data may be transferred to or from a peripheral device be transferring between the processor and an I/O module.

**Data processing:** The processor may perform some arithmetic or logic operation on data.

**Control:** An instruction may specify that the sequence of execution be altered For example, the processor may fetch an instruction from location 149, which specifies that the next instruction be from location 182. The processor will remember this fact by setting the program counter to 182. Thus, on the next fetch cycle, the instruction will be fetched from location 182 rather than 150.

An instruction's execution may involve a combination of these actions.

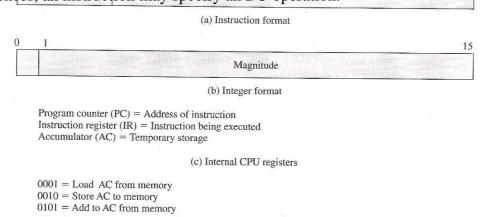

The processor contains a single data register called an accumulator (AC). Both instructions and data are 16 bits long. Thus, it convenient to organize memory using 16-bit words. The instruction format provide 4 bits for the opcode, so that there can be as many as  $2^4 = 16$  different opcodes, aup to 212 = 4096 (4K) words of memory can be directly addressed.

address 941 and stores the result in the latter location. Three instructions, which be described as three fetch and three execute cycles, are required:

- 1. The PC contains 300, the address of the first instruction. This instruction value 1940 in hexadecimal) is loaded into the instruction register IR anPC is incremented. Note that this process involves the use of a memory dress register (MAR) and a memory buffer register (MBR). For simply these intermediate registers are ignored.

- 2. The first 4 bits (first hexadecimal digit) in the IR indicate that the AC is -loaded. The remaining 12 bits (three hexadecimal digits) specify the ac (940) from which data are to be loaded.

- 3. The next instruction (5941) is fetched from location 301 and the incremented.

- 4. The old contents of the AC and the contents of location 941 are added an result is stored in the AC.

- 5. The next instruction (2941) is fetched from location 302 and the F incremented.

- 6. The contents of the AC are stored in location 941.

In this example, three instruction cycles, each consisting of a fetch cycle execute cycle, are needed to add the contents of location 940 to the contents C With a more complex set of instructions, fewer cycles would be needed. Some processors, for example, included instructions that contain more than one address. Thus the execution cycle for a particular instruction on such prop could involve more than one reference to memory. Also, instead of memory references, affrintstruction may specify an I/O operation.

(d) Partial list of opcodes Figure 3.4 Characteristics of a Hypothetical Machine

| Memory      | · CPU registers | Memory      | CPU registers |

|-------------|-----------------|-------------|---------------|

| 300 1 9 4 0 | 3 0 0 PC        | 300 1 9 4 0 | 3 0 1 PC      |

| 301 5 9 4 1 | AC              | 301 5 9 4 1 | >0003 AC      |

| 302 2 9 4 1 | → 1 9 4 0 IR    | 302 2 9 4 1 | 1940 IR       |

| 940 0 0 0 3 |                 | 940 0 0 0 3 | P             |

| 941 0 0 0 2 |                 | 941 0 0 0 2 | ]             |

| Step 1      |                 | Step 2      |               |

| Memory      | CPU registers   | Memory      | CPU registers |

| 300 1 9 4 0 | 3 0 1 PC        | 300 1 9 4 0 | 3 0 2 PC      |

| 301 5 9 4 1 | 0 0 0 3 AC      | 301 5 9 4 1 | 0 0 0 5 AC    |

| 302 2 9 4 1 | → 5 9 4 1 IR    | 302 2 9 4 1 | 5941 IR       |

| 940 0 0 0 3 |                 | 940 0 0 0 3 | 3+2=5         |

| 941 0 0 0 2 |                 | 941 0 0 0 2 |               |

| Step 3      |                 | Step 4      |               |

| Memory      | CPU registers   | Memory      | CPU registers |

| 300 1 9 4 0 | 3 0 2 PC        | 300 1 9 4 0 | 3 0 3 PC      |

| 301 5 9 4 1 | 0 0 0 5 AC      | 301 5 9 4 1 | 0005 AC       |

| 302 2 9 4 1 | → 2 9 4 1 IR    | 302 2 9 4 1 | 2941 IR       |

| 940 0 0 0 3 |                 | 940 0 0 0 3 |               |

| 941 0 0 0 2 |                 | 941 0 0 0 5 |               |

| Step 5      | · · · ·         | Step 6      |               |

For example, the PDP-11 processor includes an instruction, expressed physically as ADD B,A, that stores the sum of the contents of memory locations B into memory location A. A single instruction cycle with the following steps

- Fetch the ADD instruction.

- Read the contents of memory location A into the processor.

- Read the contents of memory location B into the processor. In order to contents of A are not lost, the processor must have at least two register storing memory values, rather than a single accumulator.

- Add the two values

- Write the result from the processor to memory location A.

Thus, the execution cycle for a particular instruction may involve more than one reference to memory. Also, instead of memory references, an instructor specify an I/O operation.

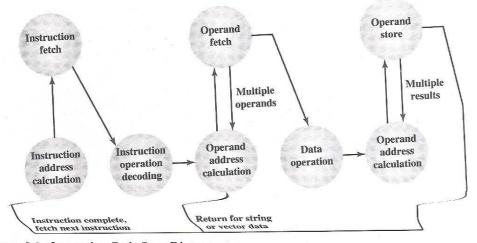

. For any given instruction cycle, some states -null and others may be visited more than once. The states can be described as follows:

**Instruction address calculation** (ac): Determine the address of the next instruction to be executed. Usually, this involves adding a fixed number to the address of the previous instruction. For example, if each instruction is 16 bits long and memory is organized into 16-bit words, then add 1 to the previous address. If, instead, memory is organized as individually addressable 8-bit bytes, then add 2 to the previous address.

Figure 3.6 Instruction Cycle State Diagram

Instruction fetch (if): Read instruction from its memory location into the processor.

**Instruction operation decoding (iod):** Analyze instruction to determine type of operation to be performed and operand(s) to be used.

**Operand address calculation (oac)**: If the operation involves reference to an operand in memory or available via I/O, then determine the address of the operand.

**Operand fetch (of):** Fetch the operand from memory or read it in from 1/O.

Data operation (do): Perform the operation indicated in the instruction. Operand store (os): Write the result into memory or out to I/O.

States in the upper part of Figure 3.6 involve an exchange between the processor and either memory or an 1/O module. States in the lower part of the diagram involve only internal processor operations. The oac state appears twice, because an instruction may involve a read, a write, or both. However, the action performed during that state is fundamentally the same in both cases, and so only a single state identifier is needed. Also note that the diagram allows for multiple operands and multiple results, because some instructions on some machines require this. For example, the PDP-11 instruction ADD A,B results in the following sequence of states: iac, if, iod, oac, of, oac, of, do, oac, os.

Finally, on some machines, a single instruction can specify an operation to be performed on a vector (one-dimensional array) of numbers or a string (one-dimensional array) of characters. As Figure 3.6 indicates, this would involve repetitive operand fetch and/or store operations.

| Table 3.1 | Classes of | Interrupu |

|-----------|------------|-----------|

| Program          | Generated by some condition that occurs as a result of an instruction<br>execution, such as arithmetic overflow, division by zero, attempt to<br>execute an illegal machine instruction, or reference outside a user's |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                  | allowed memory space.                                                                                                                                                                                                  |  |

| Timer            | Generated by a timer within the processor. This allows the operating system to perform certain functions on a regular basis.                                                                                           |  |

| 1/0              | Generated by an I/O controller, to signal normal completion of an operation or to signal a variety of error conditions.                                                                                                |  |

| Hardware failure | Generated by a failure such as power failure or memory parity error.                                                                                                                                                   |  |

# UNIT2INSTRUCTIONSETSCHARACTERISTICS AND FUNCTIONS

# **1.0 INTRODUCTION**

One boundary where the computer designer and the computer programmer can view the same machine is the machine instruction set. From the designers point of view, the machine instruction set provides the functional requirements for the processor. Implementing the processor is a tasks that in large part involves implementing the machine instruction set.

# 2.0 OBJECTIVES

At the end ;f the of this unit, you should be able to

Explain the instruction format

Understand the instruction length and characteristics

# **3.0 MAIN CONTENT**

# **3.1 INSTRUCTION FORMATS**

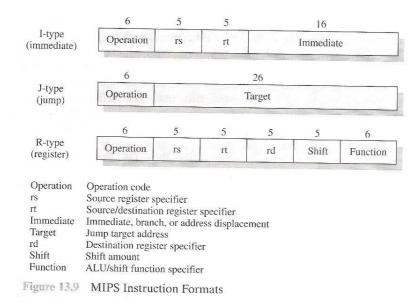

An instruction format defines the layout of the bits of an instruction, in terms of its constituent's fields. An instruction format must include an opcode and

implicitly or explicitly, zero or more operands. The format must implicitly explicitly, indicate the addressing mode for each operands. For most instruction sets, more than one instruction format is used.

## 3.1.1 INSTRUCTION LENGTH

The most basic design issue to be faced is the instruction format length. This decisions effects and is affected by, memory size, memory organization bus structure process complexity and processor speed. This decision determines the richness and flexibility of the machine.

## 3.2 INSTRUCTION SETS CHARACTERISTICS

The operation of the processor is determined by the instructions it executes referred to as machine instructions or computer instruction. The collection of different instructions that the processor can execute is referred to as the processors instruction set.

## 3.2.1 ELEMENTS OF A MACHINE INSTRUCTION

These elements are as follows:

- **Operation code:** Specifies the operation to be performed (e.g, ADD, I/O). The operation is specified by a binary code, known as the operation code or opcode.

- **Source operand reference:** This operation may involve one or more source operands, that is operands that are inputs for the operation

- **Results operands reference:** The operation may produce a result

- **Next instruction reference:** This tells the processor where to fetch the next instruction after the execution of this instruction is complete.

The address of the next instruction to be fetched could be either a real address or a virtual address, depending on the architecture. Generally, the distinction is transparent to the instruction set architecture. In most cases, the next instruction to be fetched immediately follows the current instruction. In most cases, there is no explicit reference to the next instruction when an explicit reference is needed then the main memory or virtual memory address must be supplied. Source and result operands can be in one of four areas. - **Main or virtual memory:** As with next instruction references, the main or virtual memory address must be supplied.

- **Processor register:** With rare exception a processor contains one or more registers that may be referenced by machine instructions. If only one registers exits reference to it may be implicit. If more than one register exists, then each register is assigned a unique name or number, and the instruction must contain the number of the designed register

- **Immediate:** The value of the operand is contained in a field in the instruction being executed.

- **I/O device:** The instruction must specify the I/O module and device for the operation. If memory-mapped I/O is used, this is just another main or virtual memory address

## 3.2.2 INSTRUCTION REPRESENTATION

Within the computer, each instruction is represented by a sequence of bits. The instruction is divided into fields, corresponding to the constituents elements of the instruction

Opcodes are represented by abbreviation called mnemonics that indicate the operation. Common examples include:

ADD add

| nultiply |

|----------|

|          |

DIV divide

LOAD Load data form memory

STOR Store data to memory

Operands are also represented symbolically. For example the instruction ADD, R, Y

May mean add the value contained in data location Y to the contents of register R. In this example Y refers to the address of a location in memory,

and R refers to a particular register. Note that the operation is performed on the contents of a location not on its address:

Thus, it is possible to write a machine language program in symbolic form.

A simple program would accept this symbolic input, convert opcodes and operand references to binary form, and construct binary machine instructions. However symbolic machine language remains a useful toll for describing machine instructions, and we will use it for that purpose.

Lets assume that the variables X and Y corresponds to location 413 and 414.If we assume a simple set of machine instruction, this operation could be accomplished with three instruction.

- 1. Load a register with the content of memory location 413.

- 2. Add the contents of memory location 414 to the register.

- 3. Store the contents of the register in memory location 413.

#### **3.3 INSTRUCTION SET DESIGN**

One of the most interesting and most analyzed, aspect of computer design is instruction set is very complex because it affect so many aspect of the computer system. The instruction defines any of the functions performed by the processor and thus has significant effect on the implementation of the process. The instruction set is the programmer's means of controlling the processor. Thus, programmer requirements must be considered in designing the instruction set. The most important of these fundamental design issues include the following:

- **Operation repertoire:** How many and which operations to provide and how complex operations should be.

- **Data types:** The various types of data upon which operations are perform.

- Instruction format: Instruction length (in nits) number of assesses size of various fields and so on.

- **Registers:** Number of processor registers that can be referenced by instructions and their use.

- Addressing: The mode or modes by which the address of an operand is specified.

These issues are highly interrelated and must be considered together in designing an instruction set.

## 4.0 CONCLUSION

In spite of the variety and pace of change in the computer field, certain fundamental concept applies consistently throughout. The application of these concepts depends on the current state of technology and the price/performance objectives of the designer.

#### 5.0 SUMMARY

Computer organization refers to the operational units and their interconnections that realize the architectural specification.

Computer architecture refers to those attributes of a system visible to a programmer or those attributes that have a direct impact on the logical execution of a program. Collection of different instruction that the processor can execute is referred to as the processor's instruction set and an to instruction format defines the layout of the bits of an instruction, in terms of its constituents fields.

# 6.0 TUTOR- MARKED ASSIGNMENT

1. What in general terms is the distinction between computer organization and computer architecture?

- 2. What are the four main functions of a computer

- **3.** List and briefly explain five important instruction set design issues

# 7.0 REFERENCES/ FURTHER READING

Sloss, A; symes, D; and Wright, C.ARM system developers guides an Fransisco Morgan Kaufinann, 2004

# **MODULE 2: Computer Arithmetic**

UNIT 1: The arithmetic and logic unit

UNIT 2: Control unit design/Implementation

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main content

- 3.1 The arithmetic and basic unit

- 3.2 Integer representation

- 3.3 Integer Arithmetic

- 3.4 Floating point representation

- 3.5 Floating point arithmetic

- 4.0 Conclusion

- 5.0 Summary

- 6.0 T.M.A

- 7.0 Reference and Further reading

# 1.0 INTRODUCTION

This unit focuses on the most complex aspect of the ALU, computer arithmetic. Computer arithmetic is commonly performed on two very different types of numbers: integer and floating point. In both cases, the representation chosen is a crucial design issue and is treated first.

#### 2.0 **OBJECTIVES**

At the end of this unit, you should be able to

- Understand the way in which numbers are represented (the binary format) and the algorithms used for the basic arithmetic operations (add, subtract, multiply, divide) both to integer and floating point arithmetic.

#### **3.1 THE ARITHMETIC AND LOGIC UNIT**

The arithmetic and logic unit (ALU) is that part of the computer that actually performs arithmetic and logical operations on data. All of the other elements of the computer system- Control unit, registers memory, I/0- are there mainly to bring into the ALU for it to process and then take the result back out.

An ALU and all electronic components in the computers are based on the use of simple digital logic devices that can store binary digits and perform simple Boolean logic operations.

Figure 3. 1. 1 indicates, in general terms, how the ALU is interconnected with the rest of the processor. Data are presented to the ALU in registers and the results of an operation are stored in registers. These registers are temporary storage locations within the processor that are connected by signal paths to the ALU. The ALU may also set flags as the result of an operation. For example, an overflow flag is set to 1 if the result of a computation exceeds the length of the register into which it is to be stored. The flag values are also stored in registers within the processor. The control unit provides signals that control the operation of the ALU and the movement of the data into and out of the ALU.

#### **3.2 INTEGER REPRESENTATION**

In the binary number, arbitrary numbers can be represented with just the digits zero and one the minis sign and the period or radix point.

#### $-1101.0101_2 = -13.3125_{10}$

For purposes of computer storage and processing, however w do not have the benefits of minus signs and periods. Only binary digits (0 and 1) may be used

to represent numbers. If we are limited to non negative integers, the representation is straight forward.

An 8 bit word can represent the numbers form 0 to 255, including

| 00000000 | = | 0   |

|----------|---|-----|

| 00000001 | = | 1   |

| 00101001 | = | 41  |

| 10000000 | = | 128 |

| 11111111 | = | 255 |

In general, if an n- bit sequence of binary digits is interpreted as an unsigned integer, A it value is

In going from the first to the second equation, we require that the least significant n - 1 bits do not change between the two representations. Then we get to .-next to last equation, which is only true if all of the bits in positions throem 2 are 1. Therefore, the sign-extension rule works.

#### **Fixed-point representation**

Finally, we mention that the representations discussed in this section are sometime referred to as fixed point. This is because the radix point (binary point) is fixed assumed to be to the right of the rightmost digit. The programmer can use the representation for binary fractions by scaling the numbers so that the binary poor implicitly positioned at some other location.

#### Negation

In sign-magnitude representation, the rule for forming the negation of an integer is simple: invert the sign bit. In twos complement notation, the negation of an integer can be formed with the following rules:

Take the Boolean complement of each bit of the integer (including the sign bit). That is, set each 1 to 0 and each 0 to 1.

Treating the result as an unsigned binary integer, add 1.

This two-step process is referred to as the **twos complement operation**, or the taking of the twos complement of an integer.

bitwise complement

As expected, the negative of the negative of that number is itself:

Again, interpret an n-bit sequence of binary digits a,  $-Ian-2 \dots a_l a_o$  as a twos complement integer A, so that its value is

Now form the bitwisc complement a, and, treating this is an unsigned integer, add 1. Finally, interpret the resulting n-bit sequence of binary digits as a twos complement integer *B*so that its value is

A=-2n-1a n-1 +

Some such anomaly is unavoidable. The number of different bit patterns in arn-bit word is 2n, which is an even number. We wish to represent positive and negative integers and 0. If an equal number of positive and negative integers are represented (sign magnitude), then there are two representations for 0. If there is on=\_ one representation of 0 (twos complement), then there must be an unequal numb -- - of negative and positive numbers represented..In the case of twos complement, for such an n-bit length, there is a representation for

<sup>e-</sup>~ but not for  $+2^{-1}$ .

Addition in twos complement is illustrated in Figure 9.3. Addition proceeds as it :\_ two numbers were unsigned integers. The first four examples illustrate sucreoperations. If the result of the operation is positive, we get a positive number in :-.- - complement form, which is the same as in unsigned-integer form. If the result o = : - operation is negative, we get a negative number in twos complement form. N - that, in some instances, there is a carry bit beyond the end of the word (indicat- - shading), which is ignored.

On any addition, the result may be larger than can be held in the wor- - i being used. This condition is called overflow. When overflow occurs, the ALL -- \_ signal this fact so that no attempt is made to use the result. To detect overflo-. following rule is observed:

Some insight into twos complement addition and subtraction can be gained by looking at a geometric depiction [BENH92], as shown in Figure 9.5. The circle in the upper half of each part of the figure is formed by selecting the appropriate segment of the number line and joining the endpoints. Note that when the numbers are laid out on a circle, the twos complement of any number is horizontally opposite that number (indicated by dashed horizontal lines). Starting at any number on the circle, we can add positive k (or subtract negative k), to that number by moving k positions clockwise, and we can subtract positive k (of add negative k) from that number by moving k positions counterclockwise. If an arithmetic operation results in traversal of the point where the endpoints are joined, an incorrect answer is given (overflow).

The central element is a binary adder, which is presented two numbers for addition and produces a sum and an overflow indication. The binary adder treats the two numbers as unsigned integers. For addition, the two numbers are presented to the adder from two registers, designated in this case as A and B registers. The result may be stored in one of these registers or in a third. The overflow indication is stored in a 1-bit overflow flag (0 = no overflow; I = overflow). For subtraction, the

#### **4.0 CONCLUSION**

Numbers are represented in binary form and the algorithms used for basic arithmetic operators are add, subtract, multiply and divide

#### **5.0 SUMMARY**

- An ALU and all electronic components in the digital logic devices that store binary digits and perform simple Boolean logic operations - Overflow rule occurs when two numbers positive or negative numbers are added and the result of the addition has the opposite sign.

- Subtraction flow is to subtract one number (subtracted) from another (minuend) take the two compliments (negation) of the subtrahend and hold it to the minuend.

Floating point numbers are expressed as a number (significant) multiplied by a constant (base) raised to some integer power (exponent). It can be used to represent very large and very small numbers.

#### **6.0 TUTOR- MARKED ASSIGNMENT**

What is sign- extension rule for twos compliment numbers?

Find the following differences using two compliment arithmetic:

a. 1111011 b. 10101110 c. 111110010111

-100100 -111-1-1 -111010010101

#### 7.0 Reference and further reading

Swartzlander, E. editor computer Arithimetic, volumes I and II. Los Alamitiss, CA IEEE Computer society press, 1990.

# **UNIT 2: CONTROL UNIT DESIGN/OPERATION**

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main Content

- 3.1 Micro-Operation

- 3.2 Control of the processor

- 3.3 Hard wired implementation

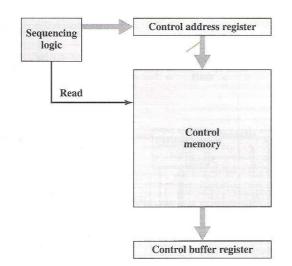

- 3.4 Micro programmed control

- 4.0 Conclusion

- 5.0 Summary

- 6.0 T. M.A

#### 7.0 Reference and further reading

#### 1.0 Introduction

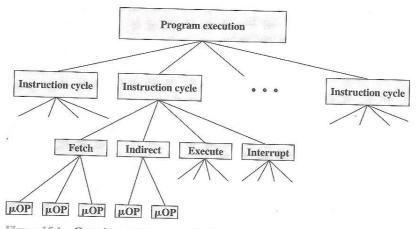

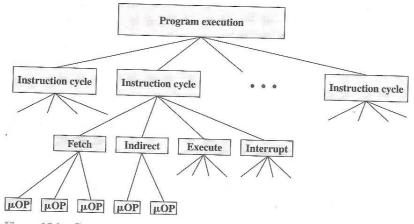

The execution of an instruction involves the execution of a sequence of sub steps, generally called cycles. For example an execution may consist of fetch, indirect, execute and interrupt cycles. Each cycle is in turn made up is a sequence of more fundamental operations called micro- operations. A single micro operation generally involves a transfer between registers a transfer between registers a register and an external bus, or a simple ALU operation.

#### 2.0 At the end of this unit you should be able to

- Understand that each cycle is in turn made up of a sequence of more fundamental operations called micro- operations.

- Identify the two task performs by the control unit of a processor which are: Generation of control signals that causes each Micro operation to be executed and causing the processor to step through a series of micro- operations in the proper sequence based on the program being executed.

#### **3.1 MICRO OPERATIONS**

The prefix micro refers to the fact that each step is very simple and accomplishes very little. To design a control unit each of the smaller cycles involves a series of step each of which involves the processor registers. We refer to these steps as micro operations. Micro operations are the functional, or atomic operations of a processor.

Three. Now, we turn to the question of how these functions are performed or, more specifically, how the various elements of the processor are controlled to provide these functions. Thus, we turn to a discussion of the control unit, which controls the operation of the processor.

We have seen that the operation of a computer, in executing a program, consists of a sequence of instruction cycles, with one machine instruction per cycle. Of course, we must remember that this sequence of instruction cycles is not necessarily the same as the *written sequence* of instructions that make up the program, because of the existence of branching instructions. What we are referring to here is the execution *time sequence* of instructions.

We have further seen that each instruction cycle is made up of a number of smaller units. One subdivision that we found convenient is fetch, indirect, execute, and interrupt, with only fetch and execute cycles always occurring.

To design a control unit, however, we need to break down the description further. In our discussion of pipelining in Chapter 12, we began to see that a further decomposition is possible. In fact, we will see that each of the smaller cycles involves

a series of steps, each of which involves the processor registers. We will refer to these steps as micro-operations. The prefix *micro* refers to the fact that each step is very simple and accomplishes very little. Figure 15.1 depicts the relationship among the various concepts we have been discussing. To summarize, the execution of a program consists of the sequential execution of instructions. Each instruction is executed during an instruction cycle made up of shorter subcycles (e.g., fetch, indirect, execute, interrupt). The execution of each subcycle involves one or more shorter operations, that is, microoperations.

Micro-operations are the functional, or atomic, operations of a processor. In this section, we will. examine micro-operations to gain an understanding of how

Figure 15.1 Constituent Elements of a Program Execution

the events of any instruction cycle can be described as a sequence of such m' operations. A simple example will be used. In the remainder of this chapter. -then show how the concept of micro-operations serves as a guide to the desi=the control unit.

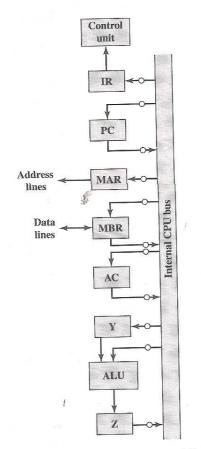

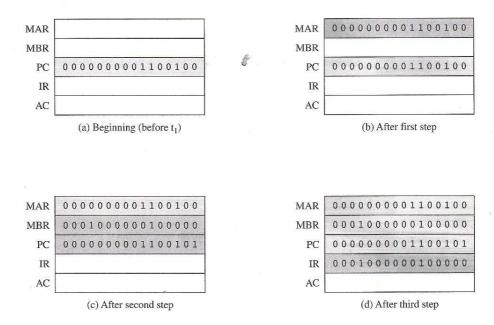

'We begin by looking at the fetch cycle, which occurs at the beginning of eac\_- \_struction cycle and causes an instruction to be fetched from memory. For purp,: of discussion, we assume the organization depicted in Figure 12.6. Four register• involved:

Memory address register (MAR): Is connected to the address lines of the tem bus. It specifies the address in memory for a read or write operation.

Memory buffer register (MBR): Is connected to the data lines of the system --\_ It contains the value to be stored in memory or the last value read from melr \_ Program counter (PC): Holds the address of the next instruction to be fete==Instruction register (IR): Holds the last instruction fetched.

Let us look at the sequence of events for the fetch cycle from the poin\_: view of its effect on the processor registers. An example appears in Figure 15.-. .=\_ the beginning of the fetch cycle, the address of the next instruction to be execs:.=-is in the program counter (PC); in this case, the address is 1100100. The first steto move that address to the memory address register (MAR) because this is only register connected to the address lines of the system bus. The second step bring in the instruction. The desired address (in the MAR) is placed on the ad c== -

We have seen that the operation of a computer, in executing a program, consists of a sequence of instruction cycles, with one machine instruction per cycle. Of course, we must remember that this sequence of instruction cycles is not necessarily the same as the *written sequence* of instructions that make up the program, because of the existence of branching instructions. What we are referring to here is the execution *time sequence* of instructions.

We have further seen that each instruction cycle is made up of a number of smaller units. One subdivision that we found convenient is fetch, indirect, execute, and interrupt, with only fetch and execute cycles always occurring.

To design a control unit, however, we need to break down the description further. In fact, we will see that each of the smaller cycles involves a series of steps, each of which involves the processor registers. We will refer to these steps as micro-operations. The prefix *micro* refers to the fact that each step is very simple and accomplishes very little. Figure 15.1 depicts the relationship among the various concepts we have been discussing. To summarize, the execution of a program consists of the sequential execution of instructions. Each instruction is executed during an instruction cycle made up of shorter subcycles (e.g., fetch, indirect, execute, interrupt). The execution of each subcycle involves one or more shorter operations, that is, micro-operations.

Micro-operations are the functional, or atomic, operations of a processor.

Figure 15.1 Constituent Elements of a Program Execution

bus, the control unit issues a READ command on the control bus, and the result appears on the data bus and is copied into the memory buffer register (MBR). We also need to increment the PC by the instruction length to get ready for the next instruction. Because these two actions (read word from memory, increment PC) do not interfere with each other, we can do them simultaneously to save time. The third step is to move the contents of the MBR to the instruction register (IR). This frees up the MBR for use during a possible indirect cycle.

Thus, the simple fetch cycle actually consists of three steps and four microoperations. Each micro-operation involves the movement of data into or out of a register. So long as these movements do not interfere with one another, several of them can take place during one step, saving time. Symbolically, we can write this sequence of events as follows:

$t_1$ : MAR E- (PC) t2: MBR <-- Memory PC <- (PC) + I t3: IR <-- (MBR)

where I is the instruction length. We need to make several comments about this sequence. We assume that a clock is available for timing purposes and that it emits regularly spaced clock pulses. Each clock pulse defines a time unit. Thus, all time units are of equal duration. Each micro-operation can be performed within the time of a single time unit. The notation  $(t_i, t_2, t_3)$  represents successive time units. In words, we have

I First time unit: Move contents of PC to MAR.

Second time unit: Move contents of memory location specified by MAR

to MBR. Increment by I the contents of the PC.

Third time unit: Move contents of MBR to IR.

Note that the second and third micro-operations both take place during the second time unit. The third micro-operation could have been grouped with the fourth without affecting the fetch operation:

t<sub>1</sub>: MAR <- (PC) t<sub>2</sub>: MBR <- Memory t3: PC E- (PC) + I IR <- (MBR) The groupings of micro-operations must follow two simple rules: The proper sequence of events must be followed. Thus (MAR - (PC)) must precede (MBR - Memory) because the memory read operation makes use of the address in the MAR.

Conflicts must be avoided. One should not attempt to read to and write from the same register in one time unit, because the results would be unpredictable. For example, the micro-operations (MBR  $\notin$ -- Memory) and (IR <- MBR) should not occur during the same time unit.

A final point worth noting is that one of the micro-operations involves an addition. To avoid duplication of circuitry, this addition could be performed by the ALU. The use of the ALU may involve additional microoperations, depending on the functionality of the ALU and the organization of the processor. We defer a discussion of this point until later in this chapter.

It is useful to compare events described in this and the following subsections to Figure 3.5. Whereas micro-operations are ignored in that figure, this discussion shows the micro-operations needed to perform the subcycles of the instruction cycle.

Once an instruction is fetched, the next step is to fetch source operands. Continuing our simple example, let us assume a one-address instruction format, with direct and indirect addressing allowed. If the instruction specifies an indirect address, then ar indirect cycle must precede the execute cycle. The data flow differs somewhat from\_ that indicated in Figure 12.7 and includes the following micro-operations:

> t<sub>1</sub>: MAR <-- (IR(Address)) t<sub>2</sub>: MBR F- Memory

t<sub>3</sub>: IR(Address) F- (MBR(Address))

The address field of the instruction is transferred to the MAR. This is then use to fetch the address of the operand. Finally, the address field of the IR is update from the MBR, so that it now contains a direct rather than an indirect address. The IR is now in the same state as if indirect addressing had not been use and it is ready for the execute cycle. We skip that cycle for a moment, to consider t interrupt cycle.

At the completion of the execute cycle, a test is made to determine whether any<sup>-</sup> :-\_abled interrupts have occurred. If so, the interrupt cycle occurs. The nature of cycle varies greatly from one machine to another. We present a very simple sequeof events, as illustrated in Figure 12.8. We have

```

t<sub>1</sub>: MBR E- (PC)

t<sub>2</sub>: MAR F- Save Address PC F-

Routine Address t<sub>3</sub>: Memory E-

(MBR)

```

In the first step, the contents of the PC are transferred to the MBR, so that ucan be saved for return from the interrupt. Then the MAR is loaded with the add- .at which the contents of the PC are to be saved, and the PC is loaded with the add to the MAR and PC, respectively. In any case, once this is done, the final step is to store the MBR, which contains the old value of the PC, into memory. The processor is now ready to begin the next instruction cycle.

The fetch, indirect, and interrupt cycles are simple and predictable. Each involves a small, fixed sequence of micro-operations and, in each case, the same micro-operations are repeated each time around.

This is not true of the execute cycle. Because of the variety opcodes, there are a number of different sequences of micro-operations that can occur. Let us consider several hypothetical examples.

First, consider an add instruction:

## ADD R1, X

which adds the contents of the location X to register R1. The following sequence of micro-operations might occur:

We begin with the IR containing the ADD instruction. In the first step, the address portion of the IR is loaded into the MAR. Then the referenced memory

location is read. Finally. the contents of RI and MBR are added by the ALLT. Again. this

is a simplified example. Additional micro-operations may be required to extract the register reference from the IR and perhaps to stage the ALt' inputs or outputs in some intermediate registers.

Let us look at two more complex examples. A common instruction is increment and skip if zero:

The content of location X is incremented by l. If the result is 0, the next instruction is skipped. A possible sequence of micro-operations is

$t_i: MAR < -- (IR(address))$   $t_2: MBR- F- Memory$   $t_z: MBR < -- (MBR) + 1$   $t_u: Memory <- (MBR)$ If ((MBR) = 0) then (PC F - (PC) + I)

The new feature introduced here is the conditional action. The PC is incremented if (MBR) = 0. This test and action can be implemented as one micro-operation. Note also that this micro-operation can be performed during the same time unit during which the updated value in MBR is stored back to memory.

It is worth pondering the minimal nature of the control unit. The control unit is the engine that runs the entire computer. It does this based only on knowing the instructions to be executed and the nature of the results of arithmetic and logical operations (e.g., positive, overflow, etc.). It never gets to see the data being processed or the actual results produced. And it controls everything with a few control signals to points within the processor and a few control signals to the system bus.

# INTERNAL PROCESSOR ORGANIZATION

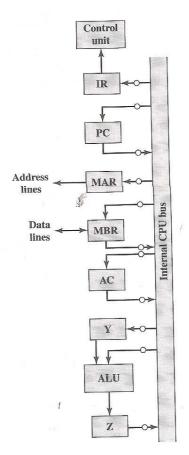

Figure 15.5 indicates the use of a variety of data paths. The complexity of this type of organization should be clear. More typically, some sort of internal bus arrangement, as was suggested in Figure 12.2, will be used.

Using an internal processor bus, Figure 15.5 can be rearranged as shown in Figure 15.6. A single internal bus connects the ALU and all processor registers.

CPU with Internal Bus.

Figure 15.6 CPU with Internal Bus

Gates and control signals are provided for movement of data onto and off the bus from each register. Additional control signals control data transfer to and from the system (external) bus and the operation of the ALU.

Two new registers, labeled Y and Z, have been added to the organization. These are needed for the proper operation of the ALU. When an operation involving two operands is performed, one can be obtained from the internal bus, but the other must be obtained from another source. The AC could be used for this purpose, but this limits the flexibility of the system and would not work with a processor with multiple general-purpose registers. Register Y provides temporary storage for the other input. The ALU is a combinatorial circuit (see Chapter 20) with no internal storage. Thus, when control signals activate an ALU function, the input to the ALU is transformed to the output. Thus, the output of the ALU cannot be directly connected to the bus, because this output would feed back to the input. Register Z provides temporary output storage. With this arrangement, an operation to add a value from memory to the AC would have the following steps:

t<sub>1</sub>: MAR <-- (IR(address)) t<sub>2</sub>: MBR E- Memory t<sub>3</sub>: Y <\_\_ (MBR) t4: Z f- (AC) + (Y) t<sub>s</sub>: AC F- (Z)

Other organizations are possible, but, in general, some sort of internal bus or set of internal buses is used. The use of common data paths simplifies the interconnection layout and the control of the processor. Another practical reason for the use of an internal bus is to save space.

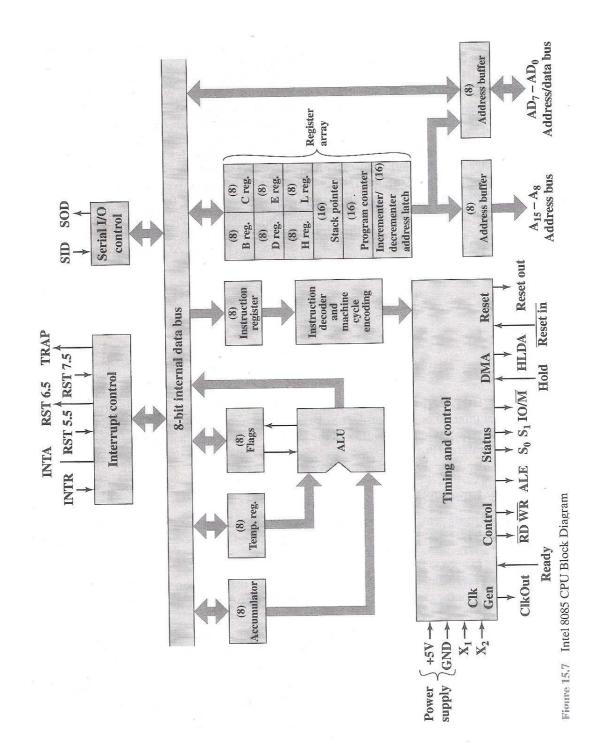

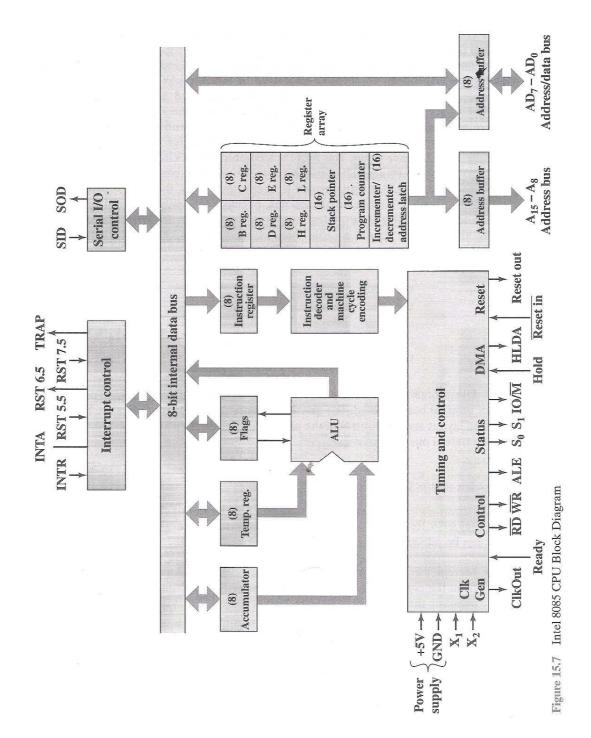

To illustrate some of the concepts introduced thus far in this chapter, let us consider the Intel 8085. Its organization is shown in Figure 15.7. Several key components that may not be self-explanatory are:

**Incrementer/decrementer address latch:** Logic that can add 1 to or subtract 1 from the contents of the stack pointer or program counter. This saves time by avoiding the use of the ALU for this purpose.

**Interrupt control:** This module handles multiple levels of interrupt signals.

**Serial I/O control:** This module interfaces to devices that communicate 1 bit at a time.

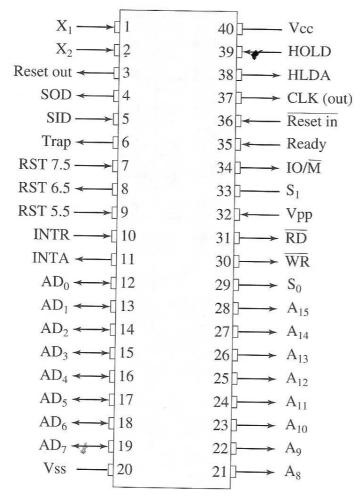

Table 15.2 describes the external signals into and out of the 8085. These are linked to the external system bus. These signals are the interface between the 8085 processor and the rest of the system (Figure 15.8).

## **Address and Data Signals**

### High Address (A15-A8)

The high-order 8 bits of a 16-bit address.

#### Address/Data (AD7-AD0)

The lower-order 8 bits of a 16-bit address or 8 bits of data. This multiplexing saves on pins.

## Serial Input Data (SID)

A single-bit input to accommodate devices that transmit serially (one bit at a time).

## Serial Output Data (SOD)

A single-bit output to accommodate devices that receive serially.

## **Timing and Control Signals**

## CLK (OUT)

The system clock. The CLK signal goes to peripheral chips and synchronizes their timing.

### X1, X2

These signals come from an external crystal or other device to drive the internal clock generator.

#### Address Latch Enabled (ALE)

Occurs during the first clock state of a machine cycle and causes peripheral chips to store the address lines. This allows the address module (e.g., memory, I/O) to recognize that it is being addressed.

#### Status (S0, S1)

Control signals used to indicate whether a read or write operation is taking place.

#### **IO/M**

Used to enable either I/O or memory modules for read and write operations.

### Read Control (RD)

Indicates that the selected memory or I/O module is to be read and that the data bus is available for data transfer.

#### Write Control (WR)

Indicates that data on the data bus is to be written into the selected memory or I/O location.

### Memory and I/O Initiated Symbols

#### Hold

Requests the CPU to relinquish control and use of the external system bus. The CPU will complete execution of the instruction presently in the IR and then enter a hold state, during which no signals are inserted by the CPU to the control, address, or data buses. During the hold state, the bus may be used for DMA operations.

#### Hold Acknowledge (HOLDA)

This control unit output signal acknowledges the HOLD signal and indicates that the bus is now available.

#### READY

Used to synchronize the CPU with slower memory or I/O devices. When an addressed device asserts READY, the CPU may proceed with an input (DBIN) or output (WR) operation. Otherwise, the CPU enters a wait state until the device is ready.

(Continued)

596 CHAPTER 15 / CONTROL UNIT OPERATION

Table 15.2 Continued

|                                                 | Interrupt-Related Signals                                                                                                                                                                                  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRAP<br>Restart Interrupts (RST                 | 7.5, 6.5, 5.5)                                                                                                                                                                                             |

| it is in the hold state or if th                | by an external device to interrupt the CPU. The CPU will not honor the request if<br>e interrupt is disabled. An interrupt is honored only at the completion of an in-<br>in descending order of priority. |

| Interrupt Acknowledge<br>Acknowledges an interr | upt.                                                                                                                                                                                                       |

|                                                 | CPU Initialization                                                                                                                                                                                         |

| RESET IN<br>Causes the contents of the          | ne PC to be set to zero. The CPU resumes execution at location zero.                                                                                                                                       |

| RESET OUT<br>Acknowledges that the O            | CPU has been reset. The signal can be used to reset the rest of the system.                                                                                                                                |

|                                                 | Voltage and Ground                                                                                                                                                                                         |

| VCC<br>+5-volt power supply                     |                                                                                                                                                                                                            |

| VSS<br>Electrical ground                        |                                                                                                                                                                                                            |

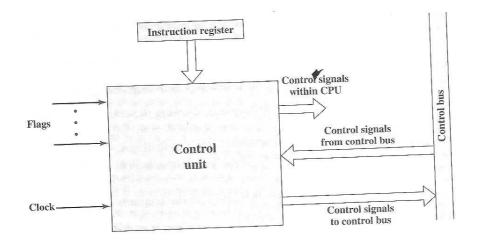

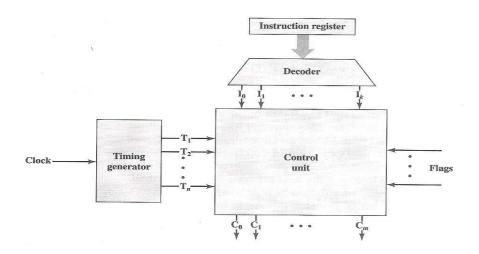

The control unit is identified as having two components labeled (1) in<sup>-</sup> decoder and machine cycle encoding and (2) timing and control. A discuss"C \_- - first component is deferred until the next section. The essence of the contthe timing and control module. This module includes a clock and accepts as i<sup>-</sup> current instruction and some external control signals. Its output consists C<sup>-</sup> : -- signals to the other components of the processor plus control signals to the :-\_- system bus.

The timing of processor operations is synchronized by the clock trolled by the control unit with control signals. Each instruction cycle i, into from one to five *machine cycles;* each

machine cycle is in turn diN from three to five states. Each state lasts one clock cycle. During a state. the

son performs one or a set of simultaneous micro-operations as determine -

control signals.

The number of machine cycles is fixed for a given instruction but one instruction to another. Machine cycles are defined to be equivalent cesses. Thus, the number of machine cycles for an instruction depends on

bar of times the processor must communicate with external devices. For e an instruction consists of two 8-bit portions, then two machine, cycles are fetch the instruction. If that instruction involves a 1-byte memory or 1/0 then a third machine cycle is required for execution.

| _                                                                                                                |      |       |                  |

|------------------------------------------------------------------------------------------------------------------|------|-------|------------------|

| X₁[]                                                                                                             | 1 4  | ob    | Vcc              |

| $X_2 \longrightarrow [2]$                                                                                        | 2 3  | 9]←── | HOLD             |

| Reset out -                                                                                                      | 3 3  | 8     | HLDA             |

| SOD <b>←</b> [] 4                                                                                                | 4 3  | 7 ]>  | CLK (out)        |

| SID →[ 5                                                                                                         | 5 3  | 6□    | Reset in         |

| Trap ←[6                                                                                                         | 5 3  | 5]→   | Ready            |

| RST 7.5 → [ 7                                                                                                    | 7 3  | 4]>   | IO/M             |

| RST 6.5 ← [8                                                                                                     | 3 3  | 3]    | $S_1$            |

| RST 5.5 [9                                                                                                       | ) 3  | 2]→   | Vpp              |

| INTR →[]                                                                                                         | 10 3 | 1 ]>  | RD               |

| INTA -[] 1                                                                                                       | 11 3 | 0]→   | WR               |

| $AD_0 \iff 1$                                                                                                    | 12 2 | 9     | $S_0$            |

| $AD_1 \leftrightarrow [1]$                                                                                       | 13 2 | 8]>   | A <sub>15</sub>  |

| $AD_2 \iff 1$                                                                                                    | 14 2 | 7]>   | A <sub>14</sub>  |

| $AD_3 \leftrightarrow [1]$                                                                                       | 15 2 | 6 →   | A <sub>13</sub>  |

| $AD_4 \iff 1$                                                                                                    | 6 2  | 5 →   | A <sub>12</sub>  |

| $AD_5 \iff 1$                                                                                                    | 7 2  | 4]>   | A <sub>11</sub>  |

| $AD_6 \iff 1$                                                                                                    | .8 2 | 3]→   | A <sub>10</sub>  |

| AD <sub>7</sub> ←→[ 1                                                                                            | .9 2 | 2]→   | A <sub>9</sub>   |

| Vss — [2                                                                                                         | 20 2 | 1 ₽→  | A <sub>8</sub> . |

| and the second |      |       |                  |

Figure 15.8 Intel 8085 Pin Configuration

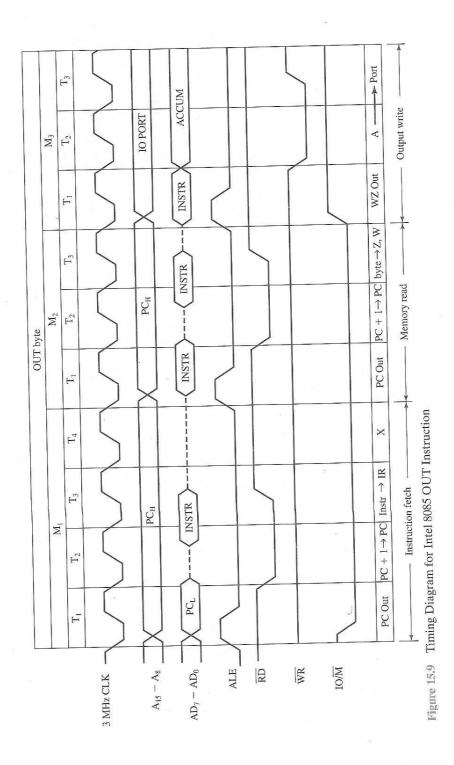

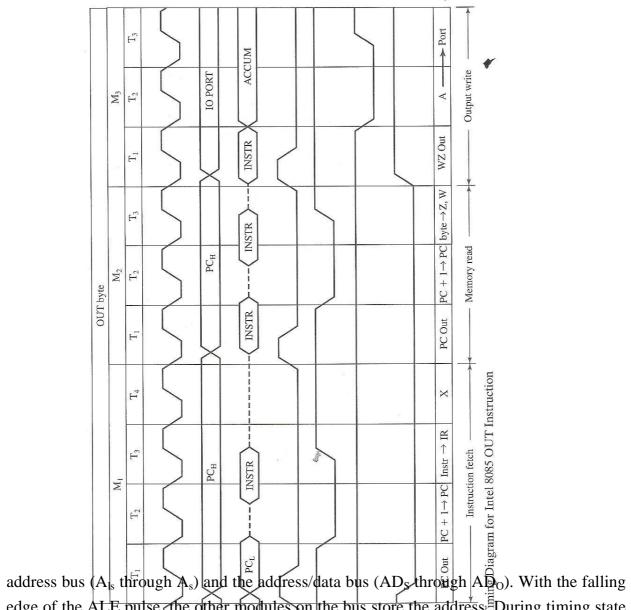

Figure 15.9 gives an example of 8085 timing, showing the value of external control signals. Of course, at the same time, the control unit generates internal control signals that control internal data transfers. The diagram shows the instruction cycle for an OUT instruction. Three machine cycles ( $M_1$ ,  $M_2$ ,  $M_3$ ) are needed. During the first, the OUT instruction is fetched. The second machine cycle fetches the second half of the instruction, which contains the number of the 1/O device selected for output. During the third cycle, the contents of the AC are written out to the selected device over the data bus.

The Address Latch Enabled (ALE) pulse signals the start of each machine cycle from the control unit. The ALE pulse alerts external circuits. During timing state  $T_1$  of machine cycle  $M_r$ , the control unit sets the IO/M signal to indicate that this is a memory operation. Also, the control unit causes the contents of the PC to be placed on the

addressed memory module places the contents of the addressed memory vocation on the address/data bus. The control unit sets the Read Control (RD) signal to indicate a read, but it waits until  $T_3$  to copy the data from the bus. This gives the memory module time to put the data on the bus and for the signal levels to stabilize. The final state,  $T_4$ , is a bus *idle* state during which the processor decodes the instruction. The remaining machine cycles proceed in a similar fashion.

Finally, consider a subroutine call instruction. As an example, consider a branchand-save-address instruction:

# BSA X

The address of the instruction that follows the BSA instruction is saved in location X, and execution continues at location X + I. The saved address will later be uses for return. This is a straightforward technique for providing subroutine calls. The fo=lowing micro-operations suffice:

t<sub>a</sub>: MAR E- (IR(address)) MBR ~ (PC)

t<sub>z</sub>: PC <-- (IR(address)) Memory <--</li>

(MBR) t<sub>3</sub>: PC <\_\_ (PC) + I</li>

The address in the PC at the start of the instruction is the address of the nexinstruction in sequence. This is saved at the address designated in the IR. The lateeaddress is also incremented to provide the address of the instruction for the next it - struction cycle.

We have seen that each phase of the instruction cycle can be decomposed into a sequence of elementary micro-operations. In our example, there is one sequence eac= for the fetch, indirect, and interrupt cycles, and, for the execute cycle, there is one sequence of micro-operations for each opcode.

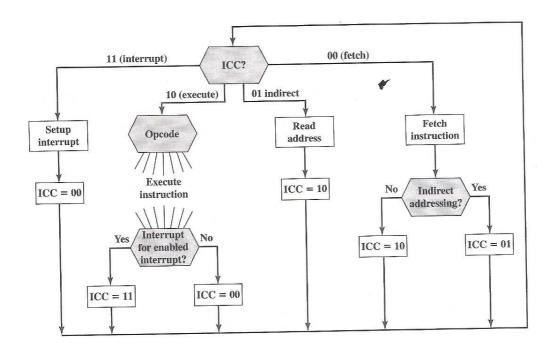

To complete the picture, we need to tie sequences of micro-operations together, and this is done in Figure 15.3. We assume a new 2-bit register called the *instruction cycle code (ICC)*. The ICC designates the state of the processor in terms of which portion of the cycle it is in:

00: Fetch 01: Indirect

10: Execute 11:

Interrupt

At the end of each of the four cycles, the ICC is set appropriately. The indirect cycle is always followed by the execute cycle. The interrupt cycle is always followed by the fetch cycle (see Figure 12.4). For both the fetch and execute cycles, the next cycle depends on the state of the system.

Thus, the flowchart of Figure 15.3 defines the complete sequence of microoperations, depending only on the instruction sequence and the interrupt pattern. Of course, this is a simplified example. The flowchart for an actual processor would be more complex. In any case, we have reached the point in our discussion in whic?, the operation of the processor is defined as the performance of a sequence of microoperations. We can now consider how the control unit causes this sequence to occur.

of tbp ~~r of the interrupt-processing routine. These two actions may each be - single micro-operation. However, because most processors provide multiple tyr\_ and/or levels of interrupts, it may take one or more additional micro-operations obtain the Save Address and the Routine Address before they can be transfer the events of any instruction cycle can be described as a sequence of such micro operations. A simple example will be used. In the remainder of this chapter, we then show how the concept of microoperations serves as a guide to the design of the control unit.

## THE FETCH CYCLE

We begin by looking at the fetch cycle, which occurs at the beginning of each instruction cycle and causes an instruction to be fetched from memory. Four registers are involved:

- Memory address register (MAR): Is connected to the address lines of the system bus. It specifies the address in memory for a read or write operation.

- Memory buffer register (MBR): Is connected to the data lines of the system bus. It contains the value to be stored in memory or the last value read from memory.

- **Program counter (PC):** Holds the address of the next instruction to be fetched.

- Instruction register (IR): Holds the last instruction fetched.

Let us look at the sequence of events for the fetch cycle from the point of view of its effect on the processor registers. An example appears in Figure 3.1.2. At the beginning of the fetch cycle, the address of the next instruction to be executed is in the program counter (PC); in this case, the address is 1100100. The first step is to move that address to the memory address register (MAR) because this is the only register connected to the address lines of the system bus. The second step is to bring in the instruction. The desired address (in the MAR) is placed on the address

bus, the control unit issues a READ command on the control bus, and the result appears on the data bus and is copied into the memory buffer register (MBR). We also need to increment the PC by the instruction length to get ready for the next instruction. Because these two actions (read word from memory, increment PC) do not interfere with each other, we can do them simultaneously to save time. The third step is to move the contents of the MBR to the instruction register (IR). This frees up the MBR for use during a possible indirect cycle.

Thus, the simple fetch cycle actually consists of three steps and four microoperations. Each micro-operation involves the movement of data into or out of a register. So long as these movements do not interfere with one another, several of them can take place during one step, saving time. Symbolically, we can write this sequence of events as follows:

where I is the instruction length. We need to make several comments about this sequence. We assume that a clock is available for timing purposes and that it emits regularly spaced clock pulses. Each clock pulse defines a time unit. Thus, all time units are of equal duration. Each micro-operation can be performed within the time of a single time unit. The notation  $(t1, t2, t_3)$  represents successive time units. In words, we have

- **First time unit:** Move contents of PC to MAR.

- Second time unit: Move contents of memory location specified by MAR to MBR. Increment by I the contents of the PC.

- Third time unit: Move contents of MBR to IR.

Note that the second and third micro-operations both take place during the second time unit. The third micro-operation could have been grouped with the fourth without affecting the fetch operation:

The groupings of micro-operations must follow two simple rules:

The proper sequence of events must be followed. Thus (MAR  $\underline{-}$  (PC)) must precede (MBR - Memory) because the memory read operation makes use of the address in the MAR.

Conflicts must be avoided. One should not attempt to read to and write from the same register in one time unit, because the results would be unpredictable. For example, the micro-operations (MBR Memory) and (IR  $\underline{E}$ - MBR) should not occur during the same time unit.

A final point worth noting is that one of the micro-operations involves an addition. To avoid duplication of circuitry, this addition could be performed by the ALU. The use of the ALU may involve additional micro-operations, depending on the functionality of the ALU and the organization of the processor.

Whereas micro-operations are ignored in that figure, this discussion shows the micro-operations needed to perform the subcycles of the instruction cycle.

Once an instruction is fetched, the next step is to fetch source operands. Continuing our simple example, let us assume a one-address instruction format, with direct and indirect addressing allowed. If the instruction specifies an indirect address, then an indirect cycle must precede the execute cycle.

The address field of the instruction is transferred to the MAR. This is then used to fetch the address of the operand. Finally, the address field of the IR is updated from the MBR, so that it now contains a direct rather than an indirect address.

The IR is now in the same state as if indirect addressing had not been used, and it is ready for the execute cycle. We skip that cycle for a moment, to consider the interrupt cycle.

At the completion of the execute cycle, a test is made to determine whether any enabled interrupts have occurred. If so, the interrupt cycle occurs. The nature of this cycle varies greatly from one machine to another. We have

> t<sub>1</sub>: MBR <-- (PC) t<sub>2</sub>: MAR <-- Save Address PC <-- Routine Address t<sub>3</sub>: Memory <-- (MBR)

In the first step, the contents of the PC are transferred to the MBR, so that they can be saved for return from the interrupt. Then the MAR is loaded with the address at which the contents of the PC are to be saved, and the PC is loaded with

the address of the start of the interrupt-processing routine. These two actions may each be a single micro-operation. However, because most processors provide multiple types and/or levels of interrupts, it may take one or more additional microoperations to obtain the Save Address and the Routine Address before they can be transferred to the MAR and PC, respectively. In any case, once this is done, the final step is to store the MBR, which contains the old value of the PC, into memory. The processor is now ready to begin the next instruction cycle.

The fetch, indirect, and interrupt cycles are simple and predictable. Each involves a small, fixed sequence of micro-operations and, in each case, the same micro-operations are repeated each time around.

This is not true of the execute cycle. Because of the variety opcodes, there are a number of different sequences of micro-operations that can occur. Let us consider several hypothetical examples.

First, consider an add instruction:

which adds the contents of the location X to register R1. The following sequence of micro-operations might occur:

t<sub>1</sub>: MAR <-- (IR(address)) t<sub>2</sub>: MBR <--Memory t<sub>3</sub>: R1 ~- (R1) + (MBR)

We begin with the IR containing the ADD instruction. In the first step, the address portion of the IR is loaded into the MAR. Then the referenced memory location is read. Finally, the contents of R1 and MBR are added by the ALU. Again, this is a simplified example. Additional micro-operations may be required to extract the register reference from the IR and perhaps to stage the ALU inputs or outputs in some intermediate registers.

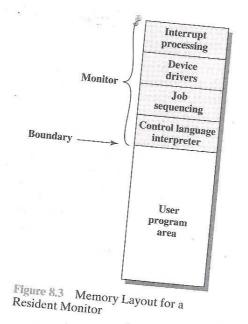

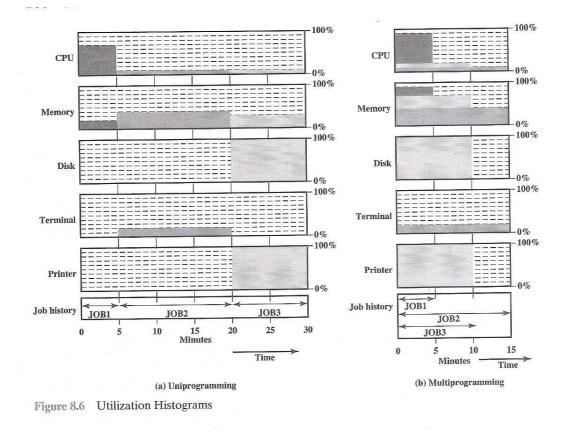

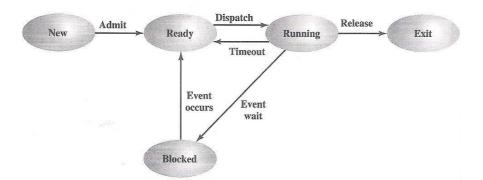

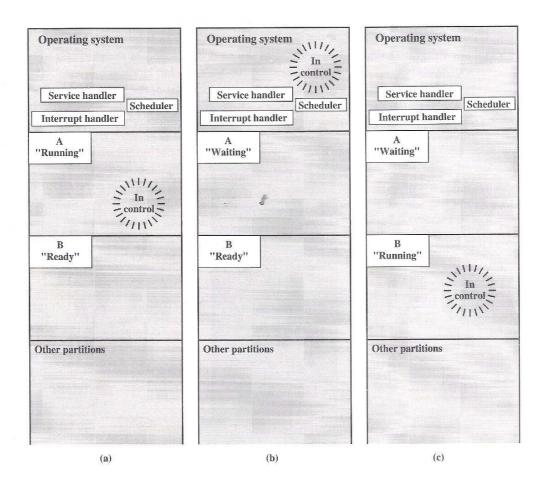

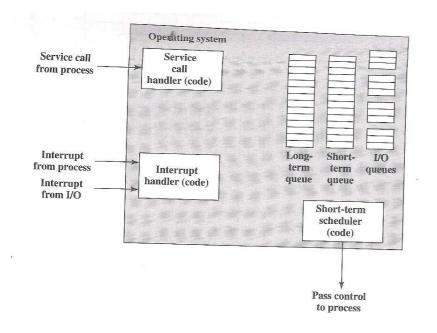

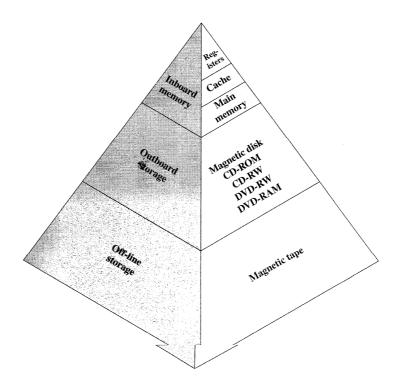

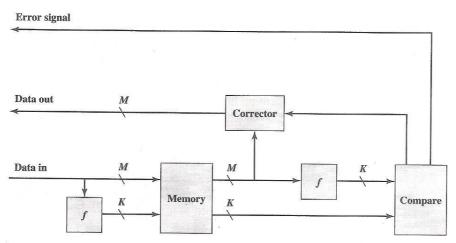

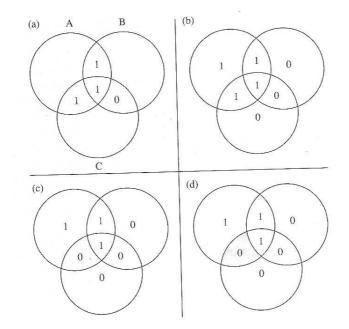

Let us look at two more complex examples. A common instruction is increment and skip if zero: